コンパレータで映像信号を取り出すところはうまくいきました。次に同期信号を分離する回路を検討します。JR-100の同期信号はかなり特殊なので、専用ICでどこまでうまく取り出せるものなのかが注目ポイントです。

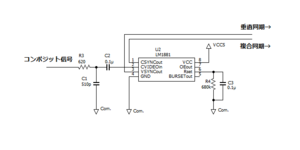

LM1881Nによる同期信号分離

同期分離にはスタンダードなLM1881Nを使います。回路はデータシートに載っているリファレンス回路そのままです。早速ここにJR-100の映像信号を入力してみます。

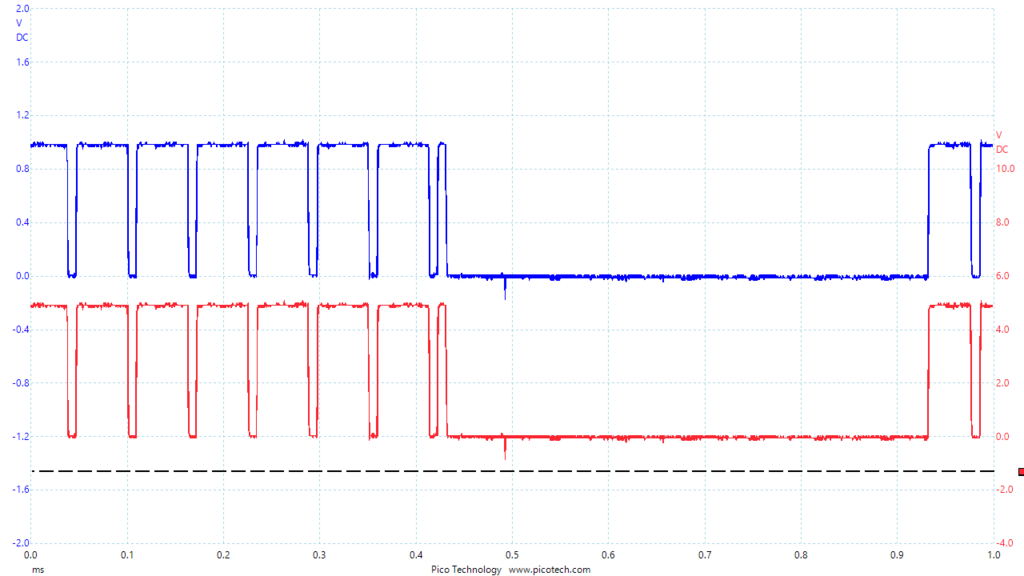

CSYNC出力

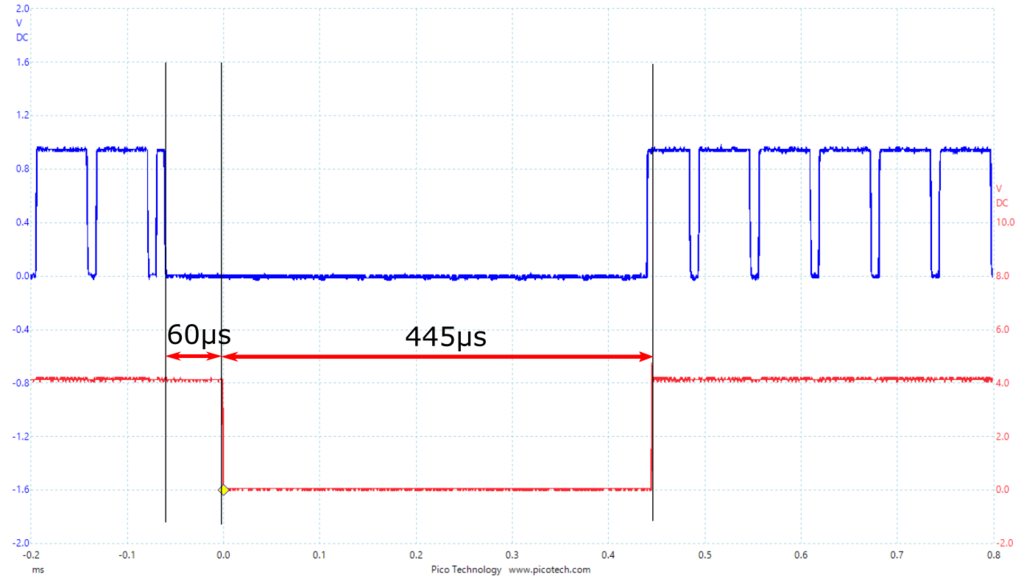

青い線が入力、赤い線がLM1881NのCSYNC出力(1番ピン)です。きれいに同期パルス部分が取り出されています。内部では単にコンパレータで一定基準以下の電圧を取り出しているだけですから当然と言えば当然。

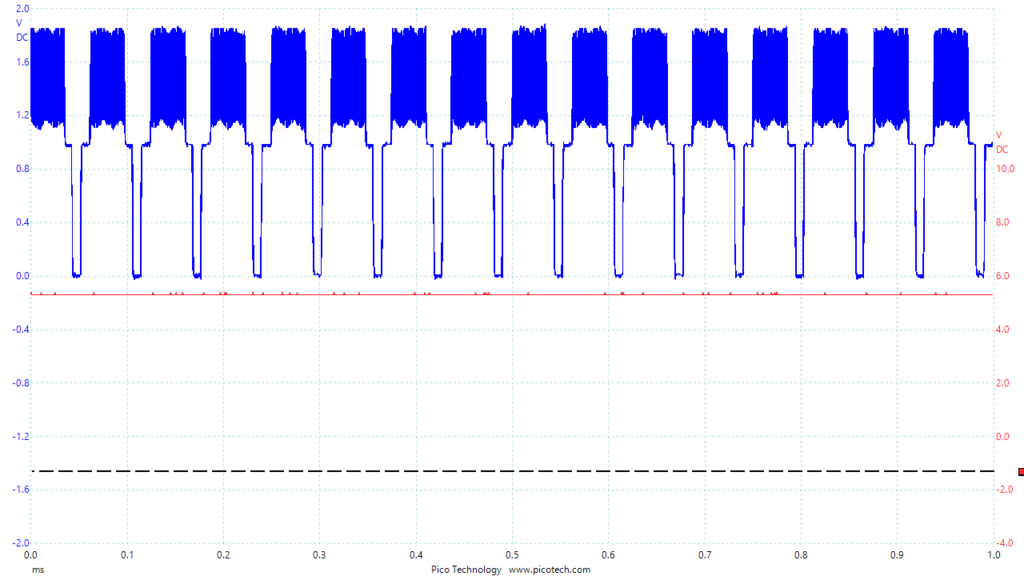

VSYNC出力

垂直同期はやはり普通とは違いました。LM1881Nのデータシートによると:

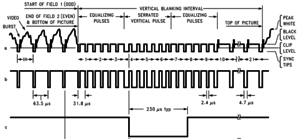

垂直同期開始直後(4フィールド目)の切り込みパルス(serration pulse)の立ち上がりでVSYNC出力がLになり、230μsの時間経過後に再度Hになる波形になるはずです。しかしJR-100の場合はそもそも切れ込みパルス自体が存在しないためか、長いパルスが始まってから60μs秒後にVSYNC出力がLになり、445μs後に(あるいはパルスの立ち上がりとともに)Hになりました。これがどういうことなのか。まずLM1881N内部の動きをデータシートで見てみます。

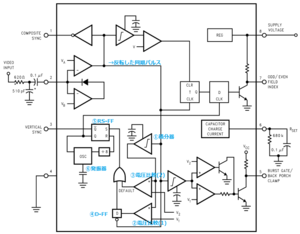

これによると、垂直同期信号の分離動作はこうです。

- 入力信号から取り出した同期信号を①積分器に入力する。積分器の入力はLowとHighが反転したものになっている。つまり同期信号がH→L→Hと変化する場合は、①積分器への入力はL→H→Lになる。

- Hになっている時間がRSETで決まる時間より長いと、①積分器の電圧が基準電圧V1を超える。

- V1を超えると②電圧比較(1)のコンパレータが動作し、④D-FF(フリップフロップ)の入力がHになる。

- この状態で入力同期パルスが立ち上がる(つまり最初の切り込みパルスが立ち上がる)とD-FFがトリガされ、⑤RS-FFのS入力がHになる。

- ⑤RS-FFのQ出力がHになり、⑥発振器が動作を開始する。発振器の周波数はRSETで決まる。このとき~Q(Qの反転出力)がLになるので、LM1881NのVSYNC出力がLになる。

- ⑥発振器が8周期分の信号を生成すると⑤RS-FFのR入力がHになりQがL(VSYNC出力がH)になる。8周期の間に入力信号の垂直同期期間が終了している(となるようにRSETを設定している)ので、①積分器の出力がLになった状態で④D-FFにラッチされており、⑤RS-FFのS入力はLになっている。(SとRが同時にHになっていない)

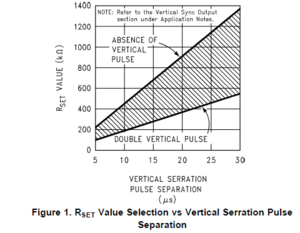

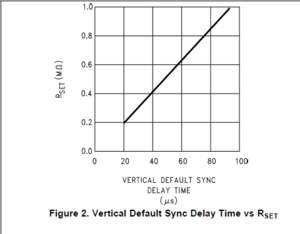

ステップ2での、①積分器の出力がV1を超えるまでの時間とRSETとの関係は下のグラフのようになります。今回はRSETとして680kΩを使っているので、15μs以上Hが続けば垂直同期とみなされます。ただし35μs以上(グラフ範囲外ですが外挿するとそれくらい)続いてしまうと別の動作が起こります。それが③電圧比較(2)で行われる電圧V2との比較に関するものです(後述)。

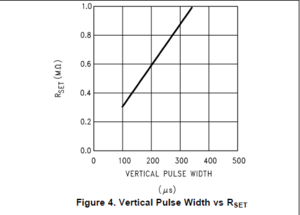

次に垂直同期のパルス幅(ステップ6での発振器8周期分の時間)を調べます。下のグラフによると、RSETが680kΩならパルス幅は230μsです。しかしJR-100での結果は445μs。誤差というには大きすぎます。

そもそもJR-100の垂直同期信号には切り込みパルスが存在しません。そこでデータシートをあらためて読んでみると、切り込みパルスが無い場合の挙動について書いてありました。

The LM1881 also generates a default vertical sync pulse when the vertical sync period is unusually long and has no serration pulses. With a very long vertical sync time the integrator has time to charge its internal capacitor above the voltage level V2. Since there is no falling edge at the end of a serration pulse to clock the “D” flip-flop, the only high signal going to the OR gate is from the default comparator when output of the integrator reaches V2. At this time the R/S flip-flop is toggled by the default comparator, starting the vertical sync pulse at pin 3 of the LM1881.

これによると、こんな動作が行われるとのことです。

- 切り込みパルスが無いと①積分器の出力電圧がV1を超えてさらにV2も超える。

- V2を超えると③電圧比較(2)のコンパレータが動作し、強制的に⑤RS-FFのS入力がHになる。

- これにより⑤RS-FFのQ出力がHになり、⑥発振器が動作を開始する。このときLM1881NのVSYNC出力はLになる。

ステップ1で①積分器の出力がV2を超えるまでの時間は下のグラフのようになります。RSETが680kΩなら約63μsとなるので、実測値60μsとほぼ一致します。

あとはパルス幅が445μsもあることの理由ですが、データシートにも該当する記載が無くよく分かりません。そこでつじつまのあう理由を考えた結果、私はこのように推定しました。

- ①積分器の電圧は、JR-100の垂直同期パルスがLで継続している間(500μs)、V2を上回る状態が続く。そのため⑤RS-FFのS入力はHを維持する。

- ⑥発振器で8周期分の時間経過後(230μs後)に⑤RS-FFのR入力をHにする。

- RS-FFのSとRが同時にHになるのは本来禁止であり結果は不定になる。LM1881Nの場合はSとRが同時にHになるとQ出力がHになるのではないか?(推定)

- もしそうならLM1881NのVSYNC出力は230μsを過ぎてもLのまま維持する。

- JR-100の垂直同期パルスが開始してから500μs後にHに変化すると、①積分器がリセットされ出力電圧がLになり、②と③のコンパレータ出力もLになる。

- すると⑤RS-FFのS入力がLになり、LM1881NのVSYNC出力がHになる。

なんか怪しいですが……。本来は禁止された入力状態に対する挙動であるため、もしかするとICごとに個体差があったり、ICマスクの新旧のリビジョン(があれば)により、結果が異なる可能性があります。

とはいえ、少なくとも手持ちのICの挙動を信じて設計していこうと思います。もしハズレのICが存在していた場合は、また別のやり方を考えます。

コメント