組み立て直後の最初の電源投入時は同期が全然合わず画面が表示されなかったり上下左右に流れてしまったりと途方に暮れる状況でした。実機デバッグでは入力信号をコントロールできないため、いろいろな場所にオシロスコープのプローブを当てて、信号の波形やタイミングが正しいかを地道にチェックするのが、ハードウェアのデバッグなんだと感じました。

さて、デバッグ終了時点での時点での実行結果を見てみます。なお今回の回路から液晶ディスプレイへの接続には、I/OデータのVABOX2を使ってます。これを通すとちゃんと映るんですが……(動画は液晶ディスプレイをiPhoneで撮影)。なおこの段階ではPICに入力する水晶発振子の周波数は3.579545MHzです。

すごくブレてます……。この現象は何だろう? 水平同期がずれている? プログラム上は間違いが無いはず。

ちょっと悩みましたが、これは、

- JR-100内部のクロック周波数(14.31818MHz)とPIC側クロック周波数(3.579545MHz)との間に微妙にずれがある。

- PICで同期信号の処理はしているが映像信号は無処理で加算

- そのため周波数の差がうねりとしてみえている。

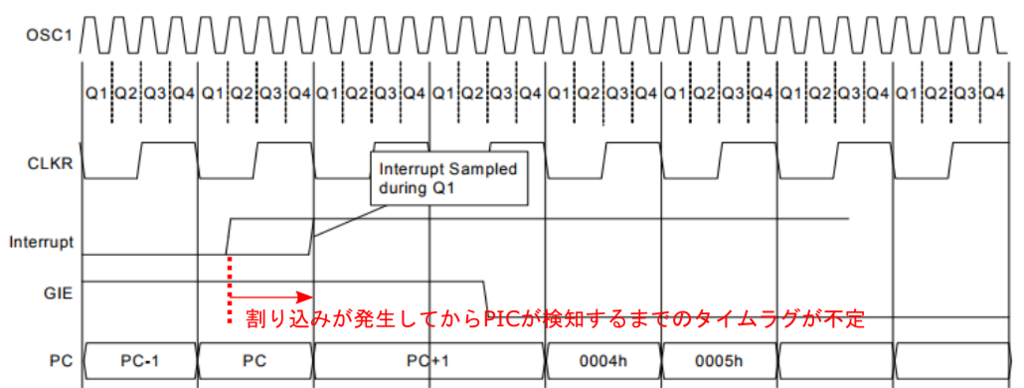

と考えました。クロック周波数がぴったり一致していれば、14.31818MHz = 3.579545 * 4 と整数倍なので、たとえ映像信号を無処理で加算したとしても映像の開始位置が左右にずれるだけでブレにはならないはずです。ところがPICの割り込み検知は命令サイクルに同期しているため、クロック周波数のズレがあると割り込み発生時点から割り込み検知までの時間は一定にはならず、0~1/Fc[秒] (Fc=PICのクロック周波数)の間で変動するものと考えられます(下図)。

PICの命令サイクルが3.579545MHzの場合、変動幅は0~279[ns]になります。画面幅を約47cm(22インチワイドディスプレイの大きさ)とすると、JR-100の1ラインあたりの時間が62.58μsであることから、279[ns]/62.58[μs]*47[cm]=約2[mm]となり、画面上で2mmの左右のブレが発生すると予測できます。実際に上のキャプチャ画面でもそれくらいのブレになっているようです。

対処療法的にこのブレを軽減するためには、クロック周波数を上げるのが簡単です。そこで水晶発振子を8MHzに変えて試してみました(もちろんPICプログラムのループカウント数もそれに合わせて修正しています)。結果は以下。

だいぶブレが小さくなりました。計算上は3.579545MHz/8MHz*2mm=0.9mmなので、ブレ幅は半分以下になるはずです。実際にはそれよりも小さい感じですけど。

このブレを根本的になくすには、次の方法が考えられます。

- JR-100内部のクロック信号を引き出してきてPICの外部クロックとする。

- 映像信号もPIC内で処理するようにし、PICが生成する同期信号起点で映像信号も生成する。

- 1画面分を一度メモリにバッファし、1画面分をまとめて出力する。

1の方法は有力ですが、なるべくJR-100内部に手を入れたくないのでちょっと保留にしたい。2の方法はPICが十分高い処理速度を持っていないと処理が間に合わないと思われるので、PIC16F1705では多分無理。3の方法はバッファリングと画像出力を並列動作させる必要があるため、これも処理速度を上げるかマルチプロセッサにしないと厳しい。ということでいずれも今回の回路の軽微な手直しではどうしようもないので、次のステップへの課題とします。

しかし一度着手したら最後までやり切ることが大切なことだと思っているので、最後の仕上げとして基板上に回路を組み立てて完成品としたいと思います。(次回に続く)

コメント

おめでとうございます!着々と進んでいらっしゃるようで、何よりです。

私はまだ電源の投入すらできていません。うらやましいようなくやしいような(笑)。

いやー、長かったですww

でもここまでくるまでに色々なことを知ることができたので、次のステップに向けてまたアイデアを練りたいと思います。

くろょさんも何か着手できる状態になったらぜひ教えてくださいね(^^